Лабораторна робота № 8

Тема: Исследование работы оперативного запоминающего устройства (ОЗУ )

1. Цель работы.

Изучить работу оперативного запоминающего устройства в режимах записи и считывания информации, исследовать временные параметры этого устройства.

Используемое оборудование и средства: персональный компьютер, среда Multisim 12 .

Краткие теоретические сведения.

Конструктивно любое ОЗУ состоит из двух блоков - матрицы запоминающих элементов и д е шифратора адреса . По технологическим соображениям матрица чаще всего имеет двухкоорд и натную дешифрацию адреса - по строкам и столбцам. На рис.1 показана матрица 16-битного ст а тического ОЗУ.

Матрица состоит из 16 ячеек памяти mem _ i .

Схема элемента матрицы (одной ячейки п а мяти) приведена на рис.2. Каждая ячейка п а мяти адресуется по входам X , Y путём выб о ра дешифраторами адресных линий по стр о кам Ах0…Ах3 и по столбцам Ау0…Ау3. Выбор осуществляется путем подачи по в ы бранным линиям матрицы сигнала лог. «1». При этом в выбранной ячейке памяти сраб а тывает двухвходовой элемент И (U 1 рис.2), подготавливая цепи чтения-записи информ а ции на входных D 10… D 13 или выходных DO0 … DO 3 разрядных шинах.

Разрешающим сигналом для выдачи адреса является CS , который подаётся на вход ра з решения счётчика адреса ( Addr _ cnt ) или т а кой же вход дешифраторов, подключённых к выходам счётчика.

Рис. 1. Матрица 16-битного ОЗУ

При записи бита в ячейку памяти (рис. 2) на соответствующей разрядной шине устанавливается 1 или 0, на входе WR /RD устанавливается «1», после стр о бирования счётчика или дешифратора адреса сигналом CS , срабатывают эл е менты 2И U 1, U 2 . Положительный пер е пад сигнала с элемента U 2 поступает на тактовый вход D -триггера U 4 , в резул ь тате чего в нём записывается 1 или 0, в з а висимости от уровня сигнала на его D -входе.

Рис. 2. Схема ячейки памяти mem _ i .

При чтении из ячейки памяти на входе WR / RD устанавливается 0, при этом срабатывают элеме н ты U 1, U 3, U 5 и на вход РАЗРЕШЕНИЕ ВЫХОДА буферного элемента U 6 поступает разреша ю щий сигнал, в результате чего сигнал с Q -выхода D -триггера передаётся на разрядную шину DO 0… DO 3.

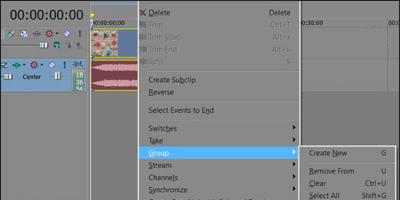

Для проверки функционирования ячейки памяти используется генератор слова (рис. 3).

Рис. 3. Лицевая панель генератора слова с установками для схемы

Для исследований режимов работы ОЗУ в лабораторной работе используется микросхема HM-65642/883, которая является ОЗУ статического типа. В отличие от ОЗУ, приведенном на рис.1, имеет объем 8192 x 8-bit ячеек.

Данные для подключения микросхемы HM-65642/883приведены на рис. 4.

Рис. 4. Обозначение выводов микросхемы ОЗУ типа НМ-65642/883.

Управление осуществляется двумя сигналами: G - разрешение выборки, W - разрешение зап и си информ а ции. Адресные входы обозначены А , выходные сигналы обозначаются буквой D .

Порядок выполнения работы.

Експеримент 1 . Исследование ячейки оперативного запоминающего устройства (ОЗУ).

Загрузить программу Multisim 12 из Главного меню.

- Соберите схему, изображенную на рис. 2.

- Изобразите какими должны быть входные и выходные сигналы на элементах И1 И6 при записи, хранении и считывании информации.

- Установите на генераторе слова комбинацию цифр, обеспечивающих запись в ячейку памяти в соответствии с номером варианта двоичной единицы.

- И6.

- Установите на генераторе слова комбинацию цифр, обеспечивающих хранение в упомянутой ячейке памяти двоичной единицы.

- Просмотрите с помощью осциллографа и зарисуйте сигналы на входах и выходах элементов И1 И6.

- Установите на генераторе слова комбинацию цифр, обеспечивающих считывание двоичной единицы с ячейки памяти.

- Просмотрите с помощью осциллографа и зарисуйте сигналы на входах и выходах элементов И1 И6.

Експеримент 2. Исследование матрицы ОЗУ .

- Соберите схему, изображенную на рис. 5.

Рис.5. Схема виртуальной платы с матрицей ОЗУ.

- С помощью клавиш S 1… S 8 задать адреса ячеек области памяти (в соответствии с номером варианта) для считывания содержимого этих ячеек. Результаты записать в виде таблицы:

Адрес Данные

К 0111

К+1 1011

К+2 1101

К+3 1110

- Записать данные с помощью клавиш S 9… S 16 в ячейки ОЗУ в соответствии с номером варианта. Данные индицируются в двоичном коде с помощью светодиодов, а адреса ячеек- с помощью цифровых индикаторов в шестнацатиричном коде.

- Данные, которые записывают в ячейки памяти в соответствии с номером варианта- следующие:

а) бегущий «0»;

б) бегущая «1»;

в) бегущие «00»;

г) бегущие «11»

д) «нарастающий уровень»;

е) «убывающий уровень»;

ж) смена тетрады «11110000»;

з) «чередование» 1010101010.

5. Динамическую индикацию осуществить при переключении клавиш адреса S 1… S 8 на соответствующие выходы счетчика, который переключает адреса ячеек в результате поступления управляющих импульсов с генератора.

6. Исследовать осциллограммы сигналов в режиме считывания данных.

1. Наименование и цель лабораторной работы.

2. Наименование каждого пункта работы, схемы, результаты измерений.

3. Выводы по результатам исследований.

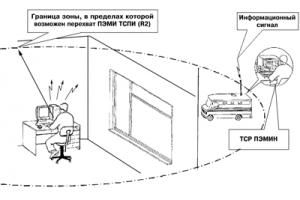

Очень часто в различных применениях требуется хранение информации, которая не изменяется в процессе эксплуатации устройства. Это такая информация как программы в микроконтроллерах, начальные загрузчики (BIOS) в компьютерах, таблицы коэффициентов цифровых фильтров в сигнальных процессорах, и , таблицы синусов и косинусов в NCO и DDS. Практически всегда эта информация не требуется одновременно, поэтому простейшие устройства для запоминания постоянной информации (ПЗУ) можно построить на мультиплексорах. Иногда в переводной литературе постоянные запоминающие устройства называются ROM (read only memory — память доступная только для чтения). Схема такого постоянного запоминающего устройства (ПЗУ) приведена на рисунке 1.

Рисунок 1. Схема постоянного запоминающего устройства (ПЗУ), построенная на мультиплексоре.

В этой схеме построено постоянное запоминающее устройство на восемь одноразрядных ячеек. Запоминание конкретного бита в одноразрядную ячейку производится запайкой провода к источнику питания (запись единицы) или запайкой провода к корпусу (запись нуля). На принципиальных схемах такое устройство обозначается как показано на рисунке 2.

Рисунок 2. Обозначение постоянного запоминающего устройства на принципиальных схемах.

Для того, чтобы увеличить разрядность ячейки памяти ПЗУ эти микросхемы можно соединять параллельно (выходы и записанная информация естественно остаются независимыми). Схема параллельного соединения одноразрядных ПЗУ приведена на рисунке 3.

Рисунок 3. Схема многоразрядного ПЗУ (ROM).

В реальных ПЗУ запись информации производится при помощи последней операции производства микросхемы — металлизации. Металлизация производится при помощи маски, поэтому такие ПЗУ получили название масочных ПЗУ . Еще одно отличие реальных микросхем от упрощенной модели, приведенной выше — это использование кроме мультиплексора еще и . Такое решение позволяет превратить одномерную запоминающую структуру в двухмерную и, тем самым, существенно сократить объем схемы дешифратора, необходимого для работы схемы ПЗУ. Эта ситуация иллюстрируется следующим рисунком:

Рисунок 4. Схема масочного постоянного запоминающего устройства (ROM).

Масочные ПЗУ изображаются на принципиальных схемах как показано на рисунке 5. Адреса ячеек памяти в этой микросхеме подаются на выводы A0 ... A9. Микросхема выбирается сигналом CS. При помощи этого сигнала можно наращивать объем ПЗУ (пример использования сигнала CS приведён при обсуждении ). Чтение микросхемы производится сигналом RD.

Рисунок 5. масочного ПЗУ (ROM) на принципиальных схемах.

Программирование масочного ПЗУ производится на заводе изготовителе, что очень неудобно для мелких и средних серий производства, не говоря уже о стадии разработки устройства. Естественно, что для крупносерийного производства масочные ПЗУ являются самым дешевым видом ПЗУ, и поэтому широко применяются в настоящее время. Для мелких и средних серий производства радиоаппаратуры были разработаны микросхемы, которые можно программировать в специальных устройствах — программаторах. В этих ПЗУ постоянное соединение проводников в запоминающей матрице заменяется плавкими перемычками, изготовленными из поликристаллического кремния. При производстве ПЗУ изготавливаются все перемычки, что эквивалентно записи во все ячейки памяти ПЗУ логических единиц. В процессе программирования ПЗУ на выводы питания и выходы микросхемы подаётся повышенное питание. При этом, если на выход ПЗУ подаётся напряжение питания (логическая единица), то через перемычку ток протекать не будет и перемычка останется неповрежденной. Если же на выход ПЗУ подать низкий уровень напряжения (присоединить к корпусу), то через перемычку запоминающей матрицы будет протекать ток, который испарит ее и при последующем считывании информации из этой ячейки ПЗУ будет считываться логический ноль.

Такие микросхемы называются программируемыми ПЗУ (ППЗУ) или PROM и изображаются на принципиальных схемах как показано на рисунке 6. В качестве примера ППЗУ можно назвать микросхемы 155РЕ3, 556РТ4, 556РТ8 и другие.

Рисунок 6. Условно-графическое обозначение программируемого постоянного запоминающего устройства (PROM) на принципиальных схемах.

Программируемые ПЗУ оказались очень удобны при мелкосерийном и среднесерийном производстве. Однако при разработке радиоэлектронных устройств часто приходится менять записываемую в ПЗУ программу. ППЗУ при этом невозможно использовать повторно, поэтому раз записанное ПЗУ при ошибочной или промежуточной программе приходится выкидывать, что естественно повышает стоимость разработки аппаратуры. Для устранения этого недостатка был разработан еще один вид ПЗУ, который мог бы стираться и программироваться заново.

ПЗУ с ультрафиолетовым стиранием строится на основе запоминающей матрицы построенной на ячейках памяти, внутреннее устройство которой приведено на следующем рисунке:

Рисунок 7. Запоминающая ячейка ПЗУ с ультрафиолетовым и электрическим стиранием.

Ячейка представляет собой МОП транзистор, в котором затвор выполняется из поликристаллического кремния. Затем в процессе изготовления микросхемы этот затвор окисляется и в результате он будет окружен оксидом кремния — диэлектриком с прекрасными изолирующими свойствами. В описанной ячейке при полностью стертом ПЗУ, заряда в плавающем затворе нет, и поэтому транзистор ток не проводит. При программировании ПЗУ, на второй затвор, находящийся над плавающим затвором, подаётся высокое напряжение и в плавающий затвор за счет туннельного эффекта индуцируются заряды. После снятия программирующего напряжения индуцированный заряд остаётся на плавающем затворе, и, следовательно, транзистор остаётся в проводящем состоянии. Заряд на плавающем затворе подобной ячейки может храниться десятки лет.

Структурная схема описанного постоянного запоминающего устройства не отличается от описанного ранее масочного ПЗУ. Единственное отличие — вместо плавкой перемычки используется описанная выше ячейка. Такой вид ПЗУ называется репрограммируемыми постоянными запоминающими устройствами (РПЗУ) или EPROM. В РПЗУ стирание ранее записанной информации осуществляется ультрафиолетовым излучением. Для того, чтобы этот свет мог беспрепятственно проходить к полупроводниковому кристаллу, в корпус микросхемы ПЗУ встраивается окошко из кварцевого стекла.

При облучении микросхемы РПЗУ, изолирующие свойства оксида кремния теряются, накопленный заряд из плавающего затвора стекает в объем полупроводника, и транзистор запоминающей ячейки переходит в закрытое состояние. Время стирания микросхемы РПЗУ колеблется в пределах 10 — 30 минут.

Количество циклов записи — стирания микросхем EPROM находится в диапазоне от 10 до 100 раз, после чего микросхема РПЗУ выходит из строя. Это связано с разрушающим воздействием ультрафиолетового излучения на оксид кремния. В качестве примера микросхем EPROM можно назвать микросхемы 573 серии российского производства, микросхемы серий 27сXXX зарубежного производства. В РПЗУ чаще всего хранятся программы BIOS универсальных компьютеров. РПЗУ изображаются на принципиальных схемах как показано на рисунке 8.

Рисунок 8. Условно-графическое обозначение РПЗУ (EPROM) на принципиальных схемах.

Так так корпуса с кварцевым окошком очень дороги, а также малое количество циклов записи-стирания привели к поиску способов стирания информации из РПЗУ электрическим способом. На этом пути встретилось много трудностей, которые к настоящему времени практически решены. Сейчас достаточно широко распространены микросхемы с электрическим стиранием информации. В качестве запоминающей ячейки в них используются такие же ячейки как и в РПЗУ, но они стираются электрическим потенциалом, поэтому количество циклов записи-стирания для этих микросхем достигает 1000000 раз. Время стирания ячейки памяти в таких ПЗУ уменьшается до 10 мс. Схема управления для электрически стираемых программируемых ПЗУ получилась сложная, поэтому наметилось два направления развития этих микросхем:

- ЕСППЗУ (EEPROM) — электрически стираемое программируемое постоянное запоминающее устройство

- FLASH-ПЗУ

Электрически стираемые ППЗУ (EEPROM) дороже и меньше по объему, но зато позволяют перезаписывать каждую ячейку памяти отдельно. В результате эти микросхемы обладают максимальным количеством циклов записи-стирания. Область применения электрически стираемых ПЗУ — хранение данных, которые не должны стираться при выключении питания. К таким микросхемам относятся отечественные микросхемы 573РР3, 558РР3 и зарубежные микросхемы EEPROM серии 28cXX. Электрически стираемые ПЗУ обозначаются на принципиальных схемах как показано на рисунке 9.

Рисунок 9. Условно-графическое обозначение электрически стираемого постоянного запоминающего устройства (EEPROM) на принципиальных схемах.

В последнее время наметилась тенденция уменьшения габаритов ЭСППЗУ за счет уменьшения количества внешних выводов микросхем. Для этого адрес и данные передаются в микросхему и из микросхемы через последовательный порт. При этом используются два вида последовательных портов — SPI порт и I2C порт (микросхемы 93сXX и 24cXX серий соответственно). Зарубежной серии 24cXX соответствует отечественная серия микросхем 558РРX.

FLASH-ПЗУ отличаются от ЭСППЗУ тем, что стирание производится не каждой ячейки отдельно, а всей микросхемы в целом или блока запоминающей матрицы этой микросхемы, как это делалось в РПЗУ.

Рисунок 10. Условно-графическое обозначение FLASH памяти на принципиальных схемах.

При обращении к постоянному запоминающему устройству сначала необходимо выставить адрес ячейки памяти на шине адреса, а затем произвести операцию чтения из микросхемы. Эта временная диаграмма приведена на рисунке 11.

Рисунок 11. Временные диаграммы сигналов чтения информации из ПЗУ.

На рисунке 11 стрелочками показана последовательность, в которой должны формироваться управляющие сигналы. На этом рисунке RD — это сигнал чтения, A — сигналы выбора адреса ячейки (так как отдельные биты в шине адреса могут принимать разные значения, то показаны пути перехода как в единичное, так и в нулевое состояние), D — выходная информация, считанная из выбранной ячейки ПЗУ.

Литература:

Вместе со статьей "Постоянные запоминающие устройства (ПЗУ)" читают:

http://сайт/digital/SintSxem.php

61 ПОЛУПРОВОДНИКОВЫЕ

ЗАПОМИНАЮЩИЕ УСТРОЙСТВА

5.2. Постоянные запоминающие устройства

5.2.1. Принципы построения схем ПЗУ

Постоянные запоминающие устройства представляют собой память с произвольным обращением, допускающую лишь считывание данных. Типовая структура ПЗУ показана на рис.5.12а. Схема ПЗУ имеет много общего со схемой ОЗУ (рис.5.5).

Рис. 5.12. ПЗУ с организацией 16 слов х 1 разряд:

а – схема, б – УГО

В узлах матрицы, образованной системой горизонтальных и вертикальных шин, включены элементы памяти - транзисторы. В качестве элементов памяти в накопителях ПЗУ могут использоваться как биполярные, так и МОП-транзисторы. Базы (затворы) транзисторов подключены к горизонтальным (адресным) шинам, эмиттеры (истоки) через перемычку соединены с вертикальными (разрядными) шинами.

Наличие перемычки означает хранение в элементе памяти 1. Если перемычка (или транзистор) отсутствуют, это означает, что в элементе хранится 0.

К адресным шинам подключены выходы дешифратора, на входы которого поступает часть разрядов адресного кода. Разрядные шины соединены с входами мультиплексора, на адресные входы которого подается вторая часть адресного кода ПЗУ. Мультиплексор имеет выход с

тремя состояниями (если G 1 = G 2 = 0 , то на выход Q проходит один из информационных сигналов, если один из сигналов не равен 0, то выход Q в третьем состоянии).

При поступлении адресного кода на одной из адресных шин Y i

установится высокий уровень напряжения, открывающий транзисторы - элементы накопителя одной строки. Транзисторы через перемычки передают высокий уровень на соответствующие разрядные шины. Если на пересечении некоторых вертикальных шин с выбранной строкой перемычки отсутствуют, то на этих шинах останется низкий уровень. Сигналы разрядных шин поступают на входы мультиплексора, который передает один из сигналов на выход Q . Какая из разрядных шин подключается к выходу, зависит от части адресного кода ПЗУ, поступающего на входы адреса мультиплексора. Таким образом, выходной сигнал ПЗУ определяется данными, хранимыми на одном из элементов накопителя.

Микросхемы ПЗУ имеют (как и ИС ОЗУ) вход выбора CS . Некоторые ИС ПЗУ имеют также вход для подачи сигнала разрешения по

входу CEO (при сигнале CEO = 1 выход переводится в третье состояние,

при CEO = 0 режим работы ПЗУ определяется сигналами на остальных входах). Условное обозначение схемы ПЗУ показано на рис. 5.12б (ROM - Read Only Memory).

Строение элемента памяти ПЗУ намного проще, чем ОЗУ. Поэтому на той же площади накопителя можно построить ЗУ с большей информационной емкостью. Записанная в ПЗУ информация сохраняется при отключении питания, что делает удобным хранение в ПЗУ стандартных программ вычислительных машин и т.п. ПЗУ можно использовать в качестве универсальной комбинационной схемы. Входные переменные схемы поступают на адресные входы ПЗУ. Значение выходной переменной, отвечающее каждой комбинации входных, должно быть записано в элементе ПЗУ с соответствующим адресом. Если таблица состояний содержит m входных переменных, то по каждому адресу записывается m -разрядное слово данных. Промышленностью

63 ПОЛУПРОВОДНИКОВЫЕ

ЗАПОМИНАЮЩИЕ УСТРОЙСТВА

выпускаются ИС ПЗУ для использования в качестве преобразования кодов, контроллеров, знакогенераторов, формирователей сигналов и т.п.

Запись данных в ПЗУ может осуществляться в процессе изготовления микросхемы. При этом с помощью специальной металлической маски в схеме накопителя формируется требуемый вариант соединения элементов памяти с разрядными шинами. Такие микросхемы памяти называют масочно-программируемыми, или масочными ПЗУ.

Примеры ИС:

К155ПР6 и К155ПР7 - преобразователи двоично-десятичного кода в двоичный и двоичного в двоично-десятичный, построены с использованием масочного ПЗУ емкостью 256 бит на основе ТТЛэлементов.

КР1610РЕ1 - масочное ПЗУ на n-МОП структурах емкостью 16384 бит (2048 слов х 8 разрядов). Время выбора - 340 нс, время выборки сигнала разрешения по выходу - 80 нс.

5.2.2. Программируемые ПЗУ

Программируемыми называют постоянные запоминающие устройства, которые допускают запись информации после изготовления микросхемы. Принцип записи данных в такие программируемые ПЗУ (ППЗУ) можно пояснить следующим образом. В исходном состоянии во всех элементах накопителя ПЗУ (рис. 5.12) установлены перемычки (например, нихромовые), что соответствует записи 1 по всем адресам. Устанавливая адрес элемента, в котором надо записать 0, и подавая в определенной последовательности повышенные импульсные напряжения на вывод питания и выход данных (часто имеется и специальный вывод для подачи напряжения программирования), можно расплавить перемычку этого элемента. Как было показано выше, отсутствие перемычки в некотором элементе и означает, что в нем записан 0. Для записи данных в ПЗУ используют специальные устройства, называемые программаторами.

Примеры ИС:

КР556РТ5 - программируемое ПЗУ на основе ТТЛ-элементов с диодами Шоттки емкостью 4096 бит (512 слов х 8 разрядов). Время выборки адреса - 80 нс.

ППЗУ с плавкими перемычками, пережигаемые мощными импульсами тока, могут программироваться только один раз. Устройства, допускающие многократную запись данных, называются репрограммируемыми ПЗУ (РПЗУ). Элементом памяти РПЗУ является лавинно-инжекционный МОП-транзистор с двумя затворами, один из

которых подключается к горизонтальной адресной шине, а второй изолирован и является плавающим. Пороговое напряжение МОПтранзистора в исходном состоянии близко к нулю. При подаче высокого уровня на затвор, соединенный с адресной шиной, транзистор открывается и на соответствующей вертикальной шине появляется сигнал, соответствующий записанной в элементе 1. При программировании прикладывается большое напряжение между стоком и истоком. Это вызывает инжекцию электрического заряда в область плавающего затвора, в результате чего пороговое напряжение МОП-транзистора увеличивается. Когда при выборке элемента на затвор через адресную шину поступает высокий уровень напряжения, транзистор остается закрытым и на соответствующей разрядной шине напряжение не увеличивается. Это означает, что в элементе записан «0». Заряд в плавающем затворе сохраняется очень долго (десятки тысяч часов). Записанная в РПЗУ информация может быть стерта, если кристалл накопителя осветить ультрафиолетовым излучением. При этом заряд плавающего затвора исчезает и во всех элементах памяти восстанавливается 1. После стирания РПЗУ может быть снова запрограммировано.

Кроме РПЗУ со стиранием ультрафиолетовым облучением, имеются устройства постоянной памяти с электрическим стиранием. В таком РПЗУ элемент памяти представляет собой МОП-структуру с изоляцией нитридом кремния.

Примеры ИС:

К573РР2 - репрограммируемое ПЗУ с электрическим стиранием. Информационная емкость 16384 бит (2048 слов х 8 разрядов). Время выборки адреса - 350 нс. Время хранения информации - не менее 15 тыс. часов.

К573РФ2 - репрограммируемое ПЗУ с ультрафиолетовым стиранием. Информационная емкость - 16384 бит (2048 слов х 8 разрядов). Время выборки адреса - 450 нс. Время хранения информации - не менее 25 тыс. часов. Микросхема имеет специальное окно для ультрафиолетового облучения (в режиме хранения оно должно быть закрыто). Условное обозначение РПЗУ приведено на рис. 5.13 (EPROM – Erasable Programmable ROM), UPR – напряжение программирования. Временные диаграммы, иллюстрирующие работу ЗУ в режиме считывания, показаны на рис. 5.14.

ЦИФРОВЫЕ УСТРОЙСТВА И МИКРОПРОЦЕССОРЫ ЧАСТЬ 2

65 ПОЛУПРОВОДНИКОВЫЕ

ЗАПОМИНАЮЩИЕ УСТРОЙСТВА

Рис. 5.13. Репрограммируемое ПЗУ К573РФ2 емкостью 16384 бит (2048 слов х 8 разрядов)

Рис. 5.14. Временные диаграммы работы РПЗУ К573РФ2 в режиме считывания

Все виды памяти, которые мы рассматривали до сих пор, имеют одно общее свойство: в них можно и записывать информацию, и считывать ее. Такая память называется ОЗУ (оперативное запоминающее устройство). Существует два типа ОЗУ: статическое и динамическое. Статическое ОЗУ конструируется с использованием D-триггеров. Информация в ОЗУ сохраняется на протяжении всего времени, пока к нему подается питание: секунды, минуты, часы и даже дни. Статическое ОЗУ работает очень быстро. Обычно время доступа составляет несколько наносекунд. По этой причине статическое ОЗУ часто используется в качестве кэш-памяти второго уровня.

В динамическом ОЗУ, напротив, триггеры не используются. Динамическое ОЗУ представляет собой массив ячеек, каждая из которых содержит транзистор и крошечный конденсатор. Конденсаторы могут быть заряженными и разряженными, что позволяет хранить нули и единицы. Поскольку электрический заряд имеет тенденцию исчезать, каждый бит в динамическом ОЗУ должен обновляться (перезаряжаться) каждые несколько миллисекунд, чтобы предотвратить утечку данных. Поскольку об обновлении должна заботиться внешняя логика, динамическое ОЗУ требует более сложного сопряжения, чем статическое, хотя этот недостаток компенсируется большим объемом.

Поскольку динамическому ОЗУ нужен только 1 транзистор и 1 конденсатор на бит (статическому ОЗУ требуется в лучшем случае б транзисторов на бит), динамическое ОЗУ имеет очень высокую плотность записи (много битов на одну микросхему). По этой причине основная память почти всегда строится на основе динамических ОЗУ. Однако динамические ОЗУ работают очень медленно (время доступа занимает десятки наносекунд). Таким образом, сочетание кэш-памяти на основе статического ОЗУ и основной памяти на основе динамического ОЗУ соединяет в себе преимущества обоих устройств.

Существует несколько типов динамических ОЗУ. Самый древний тип, который все еще используется, - FPM (Fast Page Mode - быстрый постраничный

Память 175

режим)-. Это ОЗУ представляет собой матрицу битов. Аппаратное обеспечение представляет адрес строки, а затем - адреса столбцов (мы описывали этот процесс, когда говорили об устройстве памяти, показанном на рис. 3.30, 6).

FPM постепенно замещается EDO 1 (Extended Data Output - память с расширенными возможностями вывода), которая позволяет обращаться к памяти еще до того, как закончилось предыдущее обращение. Такой конвейерный режим не ускоряет доступ к памяти, но зато увеличивает пропускную способность, выдавая больше слов в секунду.

И FPM, и EDO являются асинхронными. В отличие от них так называемое синхронное динамическое ОЗУ управляется одним синхронизирующим сигналом. Данное устройство представляет собой гибрид статического и динамического ОЗУ. Синхронное динамическое ОЗУ часто используется при производстве кэш-памяти большого объема. Возможно, данная технология в будущем станет наиболее предпочтительной и в изготовлении основной памяти.

ОЗУ - не единственный тип микросхем памяти. Во многих случаях данные должны сохраняться, даже если питание отключено (например, если речь идет об игрушках, различных приборах и машинах). Более того, после установки ни программы, ни данные не должны изменяться. Эти требования привели к появлению ПЗУ (постоянных запоминающих устройств), которые не позволяют изменять и стирать хранящуюся в них информацию (ни умышленно, ни случайно). Данные записываются в ПЗУ в процессе производства. Для этого изготавливается трафарет с определенным набором битов, который накладывается на фоточувствительный материал, а затем открытые (или закрытые) части поверхности вытравливаются. Единственный способ изменить программу в ПЗУ - поменять целую микросхему.

ПЗУ стоят гораздо дешевле ОЗУ, если заказывать их большими партиями, чтобы оплатить расходы на изготовление трафарета. Однако они не допускают изменений после выпуска с производства, а между подачей заказа на ПЗУ и его выполнением может пройти несколько недель. Чтобы компаниям было проще разрабатывать новые устройства, основанные на ПЗУ, были выпущены программируемые ПЗУ. В отличие от обычных ПЗУ, их можно программировать в условиях эксплуатации, что позволяет сократить время выполнения заказа. Многие программируемые ПЗУ содержат массив крошечных плавких перемычек. Можно пережечь определенную перемычку, если выбрать нужную строку и нужный столбец, а затем приложить высокое напряжение к определенному выводу микросхемы.

Следующая разработка этой линии - стираемое программируемое ПЗУ, которое можно не только программировать в условиях эксплуатации, но и стирать с него информацию. Если кварцевое окно в данном ПЗУ подвергать воздействию сильного ультрафиолетового света в течение 15 минут, все биты установятся на 1. Если нужно сделать много изменений во время одного этапа проектирования, стираемые ПЗУ гораздо экономичнее, чем обычные программируемые ПЗУ, поскольку их можно использовать многократно. Стираемые программируемые ПЗУ обычно устроены так же, как статические ОЗУ. Например, микросхема 27С040 имеет структуру, которая показана на рис. 3.30, а, а такая структура типична для статического ОЗУ.

Динамическая намять типа EDO вытеснила обычную динамическую память, работающую н режиме FPM, в середине 90-х годов. - Примеч. научи, ред.

Следующий этап - электронно-перепрограммируемое ПЗУ, с которого можно стирать информацию, прилагая к нему импульсы, и которое не нужно для этого помещать в специальную камеру, чтобы подвергнуть воздействию ультрафиолетовых лучей. Кроме того, чтобы перепрограммировать данное устройство, его не нужно вставлять в специальный аппарат для программирования, в отличие от стираемого программируемого ПЗУ. Но с другой стороны, самые большие электронно-перепрограммируемые ПЗУ в 64 раза меньше обычных стираемых ПЗУ, и работают они в два раза медленнее. Электронно-перепрограммируемые ПЗУ не могут конкурировать с динамическими и статическими ОЗУ, поскольку они работают в 10 раз медленнее, их емкость в 100 раз меньше и они стоят гораздо дороже. Они используются только в тех ситуациях, когда необходимо сохранение информации при выключении питания.

Более современный тип электронно-перепрограммируемого ПЗУ - флэш-память. В отличие от стираемого ПЗУ, которое стирается под воздействием ультрафиолетовых лучей, и от электронно-программируемого ПЗУ, которое стирается по байтам, флэш-память стирается и записывается блоками. Как и любое электронно-перепрограммируемое ПЗУ, флэш-память можно стирать, не вынимая ее из микросхемы. Многие изготовители производят небольшие печатные платы, содержащие десятки мегабайтов флэш-памяти. Они используются для хранения изображений в цифровых камерах и для других целей. Возможно, когда-нибудь флэш-память вытеснит диски, что будет грандиозным шагом вперед, учитывая время доступа в 100 не. Основной технической проблемой в данный момент является то, что флэш-память изнашивается после 10 000 стираний, а диски могут служить годами независимо от того, сколько раз они перезаписывались. Краткое описание различных типов памяти дано в табл. 3.2.

Таблица 3.2. Характеристики различных видов памяти

| Тип запо- | Категория | Стирание | Изменение | Энерго- | Применение |

| минающего | записи | информации | зависи- | ||

| устройства | по байтам | мость | |||

| Статическое | Чтение/ | Электрическое | Да | Да | Кэш-память |

| ОЗУ (SRAM) | запись | второго уровня | |||

| Динамическое | Чтение/ | Электрическое | Да | Да | Основная память |

| ОЗУ (DRAM) | запись | ||||

| ПЗУ(ЯОМ) | Только | Невозможно | Нет | Нет | Устройства |

| чтение | большого размера | ||||

| Програм- | Только | Невозможно | Нет | Нет | Устройства |

| мируемое | чтение | небольшого | |||

| ПЗУ (PROM) | размера | ||||

| Стираемое | Преиму- | Ультра- | Нет | Нет | Моделирование |

| програм- | щественно | фиолетовый | устройств | ||

| мируемое | чтение | свет | |||

| ПЗУ(ЕРРЮМ) | |||||

| Электронно- | Преиму- | Электрическое | Да | Нет | Моделирование |

| перепрограм- | щественно | устройств | |||

| мируемое ПЗУ | чтение | ||||

| (EEPROM) | |||||

| флэш-память | Чтение/ | Электрическое | Нет | Нет | Цифровые камеры |

| (Flash) | запись |

Микросхемы процессоров и шины 177

Микросхемы процессоров и шины

Поскольку нам уже известна некоторая информация о МИС, СИС и микросхемах памяти, то мы можем сложить все составные части вместе и изучать целые системы. В этом разделе сначала мы рассмотрим процессоры на цифровом логическом уровне, включая цоколевку (то есть значение сигналов на различных выводах). Поскольку центральные процессоры тесно связаны с шинами, которые они используют, мы также кратко изложим основные принципы разработки шин. Б следующих разделах мы подробно опишем примеры центральных процессоров и шин для них.

Микросхемы процессоров

Все современные процессоры помещаются на одной микросхеме. Это делает вполне определенным их взаимодействие с остальными частями системы. Каждая микросхема процессора содержит набор выводов, через которые происходит обмен информацией с внешним миром. Одни выводы передают сигналы от центрального процессора, другие принимают сигналы от других компонентов, третьи делают и то и другое. Изучив функции всех выводов, мы сможем узнать, как процессор взаимодействует с памятью и устройствами ввода-вывода на цифровом логическом уровне.

Выводы микросхемы центрального процессора можно подразделить на три типа: адресные, информационные и управляющие. Эти выводы связаны с соответствующими выводами на микросхемах памяти и микросхемах устройств ввода-вывода через набор параллельных проводов (так называемую шину). Чтобы вызвать команду, центральный процессор сначала посылает в память адрес этой команды по адресным выводам. Затем он запускает одну или несколько линий управления, чтобы сообщить памяти, что ему нужно, например, прочитать слово. Память выдает ответ, помещая требуемое слово на информационные выводы процессора и посылая сигнал о том, что это сделано. Когда центральный процессор получает данный сигнал, он принимает слово и выполняет вызванную команду. ■ Команда может требовать чтения или записи слов, содержащих данные. В этом случае весь процесс повторяется для каждого дополнительного слова. Как происходит процесс чтения и записи, мы подробно рассмотрим ниже. Важно понимать, что центральный процессор обменивается информацией с памятью и устройствами ввода-вывода, подавая сигналы на выводы и принимая сигналы на входы. Другого способа обмена информацией не существует.

Число адресных выводов и число информационных выводов - два ключевых параметра, которые определяют производительность процессора. Микросхема, содержащая m адресных выводов, может обращаться к 2 т ячейкам памяти. Обычно m равно 16, 20, 32 или 64. Микросхема, содержащая п информационных выводов, может считывать или записывать n-битное слово за одну операцию. Обычно п равно 8, 16, 32, 36 или 64. Центральному процессору с 8 информационными выводами понадобится 4 операции, чтобы считать 32-битное слово, тогда как процессор, имеющий 32 информационных вывода, может сделать ту же работу в одну

Глава 3. Цифровой логический уровень

операцию. Следовательно, микросхема с 32 информационными выводами работает гораздо быстрее, но и стоит гораздо дороже.

Кроме адресных и информационных выводов каждый процессор содержит выводы управления. Выводы управления регулируют и синхронизируют поток данных к процессору и от него, а также выполняют другие разнообразные функции. Все процессоры содержат выводы для питания (обычно +3,3 В или +5 В), «земли» и синхронизирующего сигнала (меандра). Остальные выводы разнятся от процессора к процессору. Тем не менее выводы управления можно разделить на несколько основных категорий:

1. Управление шиной.

2. Прерывание.

3. Арбитраж шины.

4. Состояние.

5. Разное.

Ниже мы кратко опишем каждую из этих категорий. Когда мы будем рассматривать микросхемы Pentium II, UltraSPARC II и picojava II, мы дадим более подробную информацию. Схема типичного центрального процессора, в котором используются эти типы сигналов, изображена на рис. 3.31.

ОЗУ (англ. RAM) и ПЗУ (англ. ROM) - это цифровые накопители информации. Их применяют, если внутренних ресурсов MK по тем или иным причинам недостаточно. Для сравнения, объём памяти данных MK составляет 0.5…8 Кбайт, объём памяти программ - 2…256 Кбайт. Подключить же к MK можно ещё одну или несколько внешних микросхем ОЗУ ёмкостью 32…512 Кбайт или флэш-ПЗУ ёмкостью 0.5…128 Мбайт. Увеличение вычислительных ресурсов налицо.

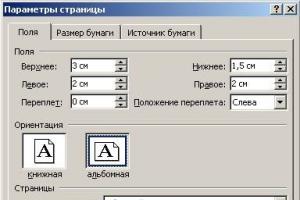

Обобщённые структурные схемы ОЗУ и ПЗУ во многом совпадают (Рис. 3.8). Базой служит прямоугольная матрица ячеек памяти, доступ к которой осуществляется через линии адреса AO…An, а чтение/запись - через двунаправленную шину данных I/OO…I/Ok. Многочисленные разновидности ОЗУ и ПЗУ отличаются друг от друга логикой формирования сигналов управления CS, WR, RD, а также наличием или отсутствием мультиплексирования адресных линий.

Рис. 3.8. Структурная схема ОЗУ (ПЗУ).

Внешние ПЗУ лучше использовать «низковольтные» электрически перезаписываемые (ключевое слово «Flash»). Напряжение программирования у них составляет 5 В в отличие от 12…27 В в старинных «высоковольтных» ПЗУ 27C256, КР573РФ6А, которые применять сейчас совместно с MK не имеет смысла.

Типовое время хранения информации в флэш-ПЗУ достигает 10…40 лет при 0.1…1 млн циклов перезаписи. Различают последовательные и параллельные флэш-ПЗУ. Первые из них малогабаритные, маловыводные, но они имеют низкую скорость доступа и невысокую ёмкость. Пример - серии 24Cxxx, 93Cxx. Для подключения таких ПЗУ к MK применяют двух или трёхпроводные интерфейсы PC, SPI. В противовес этому параллельные флэш-ПЗУ обладают большим объёмом памяти, хорошим быстродействием, но требуют для сопряжения с MK много выводов (два-три свободных 8-битных порта). Пример - серии 28Fxxx, 29Cxxx.

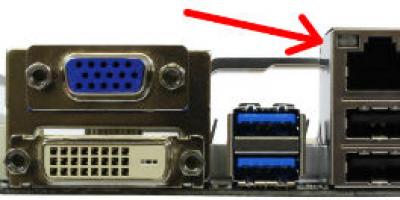

Внешние ОЗУ имеют высокую скорость записи и чтения, но информация в них теряется при выключении питания. Для сопряжения ОЗУ с MK используют обе линии портов. Иногда выгоднее их перевести в специальный режим «External RAM», при котором область внешнего ОЗУ включается в общую карту памяти. Поддерживает ли конкретный MK подобный режим, можно определить по специфическим названиям линий портов в его условном обозначении. Например, на Рис. 3.9 это «АР0»…«АР7» (шина данных/адреса), «А8»…«А15» (старшие разряды шины адреса), «ALE», «WR», «RD» (сигналы управления).

На Рис. 3.10, а…и приведены схемы подключения внешней памяти к MK.

а) микросхема DS1 (фирма Samsung) - это «интеллектуальное» перепрограммируемое ПЗУ с собственой системой команд. Применяется, в частности, в USB-накопителях;

Рис. 3.9. Расположение выводов и названия сигналов в MK Atmel ATmega8515.

б) 16-разрядная информация в динамическом ОЗУ DS1 (фирма OKI) передаётся/принимается через выводы «1/01»…«1/04» последовательно во времени четырьмя блоками;

Рис. ЗЛО. Схемы подключения внешней памяти к MK (продолжение):

в) шина адреса «А0»…«А18» и шина данных «Ю0»…«Ю7» статического ОЗУ DS1 (фирма Samsung) мультиплексируются регистрами DD1, DD2. По фронтам сигналов F1, F2 в регистрах за два раза защёлкивается полный адрес ячейки. Недостающие адреса формируются прямо от MK («R0»…«R2»). При чтении/записи ОЗУ («*RD»/«*WR») работают 8 верхних линий MK;

г) DS1 - это ферроэлектрическое последовательное «ОЗУ/ПЗУ» FRAM (фирма Ramtron), подключаемое к MK по шине PC. При поданном питании FRAM эквивалентна ОЗУ, а при выключенном - ПЗУ. Число перезаписей не ограничено (!), время хранения информации 45 лет;

д) подключение последовательного ОЗУ DS1 (64Kx8) к MK через трёхпроводной интерфейс и «антизвонные» резисторы R2…R4;

Рис. 3.10. Схемы подключения внешней памяти к MK (продолжение):

е) в регистре DD1 хранятся младшие 8 бит шины адреса. Старшие 7 бит подаются от MK непосредственно на ОЗУ DS1 фирмы Hitachi. MK работает в режиме «External RAM». На вход «СЕ» ОЗУ DS1 вместо общего провода можно подать сигнал разрешения со свободного выхода MK. Это позволяет снизить общий расход энергии от источника питания, поскольку при ВЫСОКОМ уровне на входе «СЕ» микросхема DS1 переходит в экономичный режим хранения данных;

ж) подключение к MK последовательного флэш-ОЗУ DS1 фирмы Atmel. Если переключатель S1 замкнут, то в ОЗУ нельзя записывать данные, это режим защиты. Резисторы R3, R4 в некоторых схемах отсутствуют. Замена DS1 - любое ОЗУ большей/меньшей ёмкости из семейства DataFlash AT45DB фирмы Atmel, включая устаревшие модели AT45DB081B-CNU;

Рис. 3.10. Схемы подключения внешней памяти к MK (окончание):

з) при прямом подключении флэш-ПЗУ DS1 (фирма AMD) к MK требуется большое количество свободных линий портов. Некоторые выходные линии MK, например, «А7», могут быть одновременно задействованы для управления другими узлами, однако делать это допускается только тогда, когда отсутствует обращение к ПЗУ, т.е. при ВЫСОКОМ уровне сигнала «ОЕ»;

и) увеличение ёмкости ОЗУ за счёт параллельного соединения микросхем DSl…DSn. Каждое из подключённых ОЗУ имеет собственный сетевой программный адрес, который определяется разными логическими уровнями на входах «АО», «А1», «А2».